Halbleiterfertigung: TSMCs 3-Nanometer-Prozess steigert Leistung um 15 Prozent

TSMC hat die Eigenschaften des kommenden N3-Prozesses offengelegt, mit dem ab 2022 Siliziumchips in Serie gefertigt werden sollen.

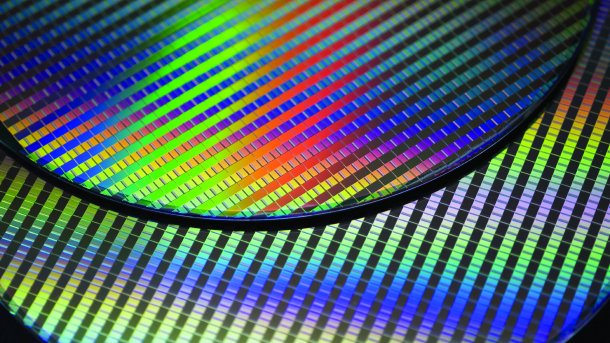

(Bild: Taiwan Semiconductor Manufacturing Co., Ltd.)

Auf die aktuell laufenden Fertigungsgenerationen mit Strukturen von 7 und 5 Nanometern folgt 3-nm-Technik. TSMC hat die Eigenschaften seines N3-Prozesses auf dem eigenen Technology Symposium verraten: Verglichen mit N5 steigt die Leistung bei gleichem Stromverbrauch um 10 bis 15 Prozent, alternativ sinkt die Leistungsaufnahme bei gleicher Performance um 25 bis 30 Prozent.

Transistoren in Logikblöcken sollen laut TSMCs Mitteilung 41 Prozent weniger Platz einnehmen (70 Prozent höhere Dichte), allerdings skalieren SRAM-Speicherzellen mit gerade einmal 25 Prozent gestiegener Dichte deutlich schlechter. Das gesamte Platzersparnis dürfte bei Prozessoren und Grafikchips mit hohen Cache-Anteilen also eher niedrig ausfallen.

Videos by heise

TSMC setzt beim N3-Prozess noch einmal auf FinFET-Transistoren, bevor ein Wechsel zum neuen Gate-All-Around-(GAA-)Design erfolgt, wie die Webseite Anandtech berichtet. Die Risikoproduktion mit 3-nm-Strukturen soll nächstes Jahr anlaufen; die Serienfertigung hat TSMC für das zweite Halbjahr 2022 angesetzt.

Alternativ N5P und N4

Für AMD, Nvidia und künftig auch Intel könnten verbesserte Versionen der 5-nm-Generation wirtschaftlich interessanter sein. TSMC bietet zeitnah den N5P-Prozess an, der verglichen mit N5 die Leistungsaufnahme um weitere 7 Prozent senkt beziehungsweise die Leistung um 4 Prozent steigert. Verglichen mit N7 verringert N5P also die Leistungsaufnahme um 40 Prozent oder verbessert die Performance um 20 Prozent.

Ferner läuft die Entwicklung eines weiteren Zwischenschrittes, N4 genannt, besser als geplant. Die Serienproduktion soll jetzt schon bis Ende 2022 und nicht erst 2023 beginnen. Die Designregeln sollen sich beim Wechsel von N5 auf N4 nur geringfügig ändern, sodass TSMC einen attraktiven Upgrade-Pfad für Chiphersteller sieht. Leistungseigenschaften nennt der Halbleiterfertiger noch nicht.

(mma)