Chipauftragsfertiger TSMC: Chips mit 3 Nanometern 2022, 2 Nanometer ab 2025

Die drei nächsten Fertigungsprozesse von TSMC befinden sich im Zeitplan: In der zweiten Jahreshälfte startet zunächst die Serienproduktion mit 3 nm.

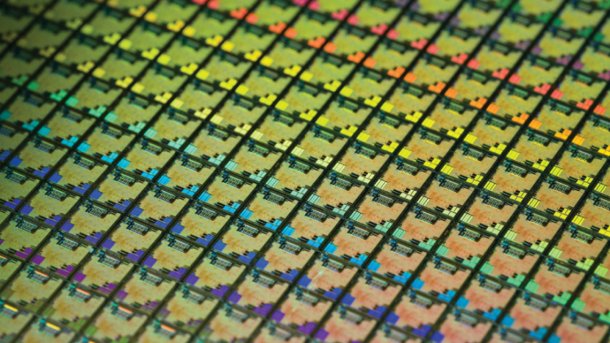

(Bild: Taiwan Semiconductor Manufacturing Co., Ltd.)

Der weltweit größte Chipauftragsfertiger TSMC bringt bis 2025 drei neue Fertigungsprozesse, wenn alles nach Plan läuft. Noch in diesem Jahr steht der Wechsel auf N3 mit 3-Nanometer-Strukturen an, zu dessen ersten Kunden traditionell Apple gehört.

Die ersten 3-nm-Prozessoren für den Retail-Markt dürften allerdings noch etwas auf sich warten lassen: Apples nächste Prozessorgeneration – die M2-Serie für neue MacBooks und der A16 für das iPhone 14 Pro – werden mit 4-nm-Strukturen erwartet, erst die Nachfolger M3 und A17 sollen mit 3-nm-Technik erscheinen. CPUs und GPUs für Desktop-PCs und Notebooks folgen üblicherweise später, mit AMD, Intel und Nvidia als wahrscheinliche Abnehmer.

Videos by heise

Der N3-Prozess verkleinert die Transistoren verglichen mit dem 5-nm-Prozess N5 laut TSMC um bis zu 70 Prozent. Wahlweise steigt die Geschwindigkeit entsprechender Chips bei gleicher Leistungsaufnahme um 15 Prozent oder die Leistungsaufnahme sinkt bei gleicher Geschwindigkeit um 30 Prozent.

N3E als Ergänzung

Ein Jahr nach dem ersten 3-nm-Prozess N3 folgt die abgewandelte Version N3E, die die Effizienz weiter erhöhen, die Designregeln etwas lockern und die Ausbeute funktionstüchtiger Chips verbessern soll. Zur Bekanntgabe der jüngsten Geschäftszahlen sagte TSMC-Chef C. C. Wei in der Analystenkonferenz (PDF), dass sich der N3E-Prozess vor dem anvisierten Zeitplan befindet.

Die Analystenfirma Morgan Stanley erwartet, dass die Serienproduktion schon im zweiten Quartal 2023 anlaufen könnte. Laut einer Kurzmitteilung (via Twitter) nimmt TSMC Änderungen an vier Layern vor, die mit älterer Immersionslithografie anstelle von extrem-ultravioletten (EUV-)Wellenlängen belichtet werden sollen. Auf der Kehrseite würde das die Transistordichte um rund 8 Prozent verringern, sodass der Vorteil gegenüber N5 bei nur noch 60 Prozent läge – CPUs und GPUs etwa würden dann etwas mehr Chipfläche benötigen als beim N3-Prozess.

N2 ab 2025

Die Risikoproduktion mit 2-nm-Strukturen plant TSMC derweil für 2024, woraufhin 2025 die Serienproduktion folgen soll. Wei erwartet letztere bis zum Jahresende 2025, sodass entsprechende Prozessoren ab Anfang 2026 in Produkten erscheinen sollten. Der N2-Prozess bringt die größte Änderung seit der 14/16-nm-Generation mit deren dreidimensionalen FinFET-Transistoren: Beim Nachfolger Gate All Around (GAA) umgibt die Gate-Elektrode den leitenden Kanal des Feldeffekttransistors (FET) allseitig. Zu den relativen Vorteilen in Sachen Transistordichte, Geschwindigkeit und Effizienz äußert sich TSMC noch nicht.

Im Jahr 2025 soll bei Intel die 18A-Serienproduktion laufen. Beide Firmen wollen zu diesem Zeitpunkt den besten Fertigungsprozess anbieten – der Wettkampf wird da spannend.

(mma)