IBM Power9 soll bei PCI Express 4.0 in Führung gehen

In der zweiten Jahreshälfte sollen Power9-Maschinen erscheinen und nicht bloß mit 24 starken CPU-Kernen glänzen, sondern auch mit PCIe 4.0, OpenCAPI 3.0 und NVLink 2.0.

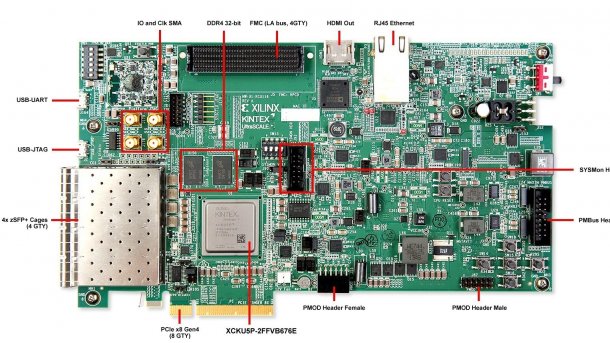

PCI-Express-4.0-Entwicklerboard mit Xilinx Kintex UltraScale+

(Bild: Xilinx)

Eigentlich treibt Intel die Entwicklung bei PCI und PCI Express seit Jahren voran, doch bei PCIe 4.0 will IBM in Führung gehen: Power- und OpenPower-Server mit dem neuen Power9, die im zweiten Halbjahr erscheinen sollen, dürften die ersten Systeme mit PCIe 4.0 sein. Pro Lane verdoppelt sich die Transferrate dabei im Vergleich zu PCIe 3.0, also von 8 GBit/s auf 16 GBit/s oder anders ausgedrückt von knapp unter 1 GByte/s auf fast 2 GByte/s (128/132-Codierung).

Mellanox hat seit dem vergangenen Herbst den 100-Gigabit/s-Ethernet-(100GbE-)Adapter ConnectX 5 mit PCIe 4.0 im Angebot, nun kündigt Xilink die FPGA-Familie UltraScale+ mit PCIe 4.0 an. Mit Prototypen haben IBM und Xilinx bereits Daten mit 16 GT/s zwischen einem solchen FPGA und einem Power9 erfolgreich getestet.

(Bild: IBM)

Hoher Durchsatz ist vor allem für Anwendungsbeschleuniger wichtig, etwa für GPU- oder FPGA-Karten für AI-/KI-Anwendungen. Dafür unterstützt der Power9 auch das Cache-kohärente Protokoll CAPI 2.0 über PCIe 4.0. Mit OpenCAPI 3.0 steht beim Power9 außerdem noch ein Interface mit 25 GBit/s pro Lane bereit. Diese 48 "BlueLink"-Lanes lassen sich als NVLink 2.0 auch für Tesla-Beschleuniger von Nvidia nutzen.

AMD und Intel unklar

Intel verspricht derzeit keine konkreten Starttermine für Xeons mit PCIe 4.0. "Mitte Sommer" sollen bekanntlich die ersten Sykale-SP-Systeme erscheinen, dabei ist bisher nicht die Rede von PCIe 4.0, ebensowenig wie bei AMD Naples. Vermutlich wird es also 2018, bis Intels Ice Lake-SP beziehungsweise AMD Starship kommen und möglicherweise PCIe 4.0 auch in x86-Servern nutzbar wird. Bisher findet sich auf Intels Server lediglich die Spezifikation für PIPE 4.4.1: Sie beschreibt zentrale Anforderungen an PHY-Bausteine oder -Funktionsblöcke, die PCIe 4.0, USB 3.1 SuperSpeedPlus oder SATA 6G übertragen (PHY Interface for PCI Express, SATA, and USB 3.1 Architectures).

Intel hat aber noch eine proprietäre Lösung für höhere Transferraten, nämlich die Omni-Path Architecture (OPA) – direkt integriert in Varianten kommender Skylake-SP-Xeons und einigen Xeon Phi.

Interface-Wettbewerb

2016 tauchten mit Gen-Z und CCIX noch zwei weitere schnelle Interface-Konzepte zur Einbindung von Rechen- und KI-Beschleunigern oder auch verteiltem Speicher in modulare Server auf. Hier steht in den nächsten Jahren ein Wettbewerb zwischen verschiedenen Schnittstellen bevor. (ciw)