FPGA-Beschleuniger als Sicherheitsrisiko

Security-Experten haben untersucht, wie sich (Intel-)FPGAs in (Cloud-)Servern für Seitenkanalangriffe wie Rowhammer einspannen lassen.

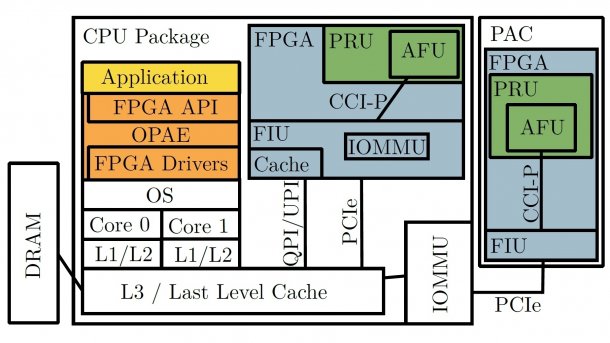

Intel Xeon mit integriertem FPGA und per PCIe angebundene PAC

(Bild: Zane Weissman, Thore Tiemann, Daniel Moghimi, Evan Custodio, Thomas Eisenbarth, Berk Sunar)

Neue Technik, neue Risiken: Programmierbare Logikchips, die als Rechenbeschleuniger beispielsweise für KI-Algorithmen in (Cloud-)Servern zum Einsatz kommen, lassen sich auch für Seitenkanalangriffe etwa auf den Hauptspeicher einspannen. Das zeigt eine Studie von sechs Sicherheitsexperten vom Worcester Polytechnic Institute, der Uni Lübeck und von Intel.

Der Paper-Titel "JackHammer: Efficient Rowhammer on Heterogeneous FPGA-CPU Platforms" nimmt das Ergebnis vorweg: In Field Programmable Gate Arrays (FPGAs) lassen sich nicht bloß nützliche Algorithmen effizient als Hardware-Verschaltung implementieren, sondern auch Malware. Beispielsweise via PCI Express (PCIe) hat ein solches FPGA Zugriff auf das RAM des Servers, je nach Implementierung auch auf den Last Level Cache (LLC) der CPU. Die Experten haben sowohl einen speziellen Intel Xeon mit integriertem, also eng angebundenem FPGA untersucht als auch einen PCIe-FPGA-Rechenbeschleuniger mit Arria 10 GX, den Intel als Programmable Acceleration Card (PAC) vermarktet – als Konkurrenz etwa zu Xilinx Alveo.

Cache-Attacken und Rowhammer

Von der PAC-Karte aus gelangen den Sicherheitsforschern keine Angriffe auf den Cache des Hauptprozessors. Doch das in die CPU integrierte FPGA konnte per "Prime & Probe" Daten aus dem LLC lesen.

Zudem war es sehr einfach, den gemeinsam genutzten, lokalen Cache des FPGA zu lesen, wenn zwei FPGA-Kerne, sogenannte Accelerator Functional Units (AFUs), gleichzeitig auf demselben FPGA liefen. Das könnte bei künftigen "Multi-Tenant"-FPGA-Angeboten von Cloud-Dienstleistern der Fall sein, wo mehrere externe Nutzer ihre AFUs auf demselben FPGA-Chips ausführen.

Vor allem jedoch ließ sich die PAC-Karte für effiziente Rowhammer-Angriffe auf Daten im Hauptspeicher (DRAM) des Servers nutzen. Diese gelangen trotz des "Umwegs" via PCIe und DMA Redirection (DMA-R, IOMMU) deutlich schneller als mit Software, die auf der CPU lief, in der wiederum der Speicher-Controller steckt.

FPGA-Sicherheit

Die Sicherheitsexperten empfehlen, bei der Einbindung von FPGAs als Rechenbeschleuniger genau auf die Sicherheit zu achten. Aktuelle FPGAs enthalten Funktionen wie Verschlüsselung und digitale Zertifikate, um nur signierten AFU-Code auszuführen, aber auch um diesen Code durch Verschlüsselung vor unbefugten Betrachtern zu schützen.

Lesen Sie mehr zum Thema Rowhammer bei heise+:

- Weshalb Rowhammer-Angriffe auf den Arbeitsspeicher funktionieren können (kostenpflichtig)

(ciw)