Mit AMD-Technik: Cray baut 1,5-Exaflops-Superrechner für Oak Ridge

Ziel Top500-Spitze: Der 1,5-EFlops-Bolide "Frontier" startet 2021 mit AMD Epyc, Radeon Instinct und Infinity Fabric am US-Nationallabor Oak Ridge.

(Bild: AMD)

2021 wird sehr spannend für AMD und Intel: Am Oak Ridge National Laboratory (ORNL) geht dann Crays "Frontier"-Supercomputer mit 1,5 Exaflops Rechenleistung nur aus AMD-Chips in Betrieb. Ebenfalls für 2021 schon geplant ist auch "Aurora" mit Intel-Technik – wiederum von Cray gebaut.

Während bei Aurora bisher nur von einer Rechenleistung im Exaflops-Bereich die Rede ist, legt sich AMD schon auf 50 Prozent mehr fest. Und für den Auftraggeber, das US-Department of Energy (DoE), hat das militärisch und geopolitisch bedeutsame Supercomputer-Wettrüsten gegen China höchste Priorität. Dafür fließen auch hunderte Millionen US-Dollar Fördermittel unter anderem an AMD, Cray, IBM, Intel und Nvidia.

(Bild: AMD)

Sowohl Aurora am Argonne National Lab (ANL) als auch Frontier nutzen Crays "Shasta"-Konzept für die Hochgeschwindigkeitsverbindung zwischen den einzelnen Cluster-Knoten (Slingshot). Intern wiederum arbeiten sowohl Frontier als auch Aurora mit Kombinationen aus Prozessoren und Rechenbeschleunigern: Bei AMD sind das ein speziell optimierter Epyc mit kommenden Zen-2- oder Zen-3-Kernen sowie je vier Radeon-Instinct-Beschleuniger pro CPU. Intel hingegen will die für 2020 angekündigten Xe-GPUs verwenden sowie selbstverständlich die dann aktuellen Xeons.

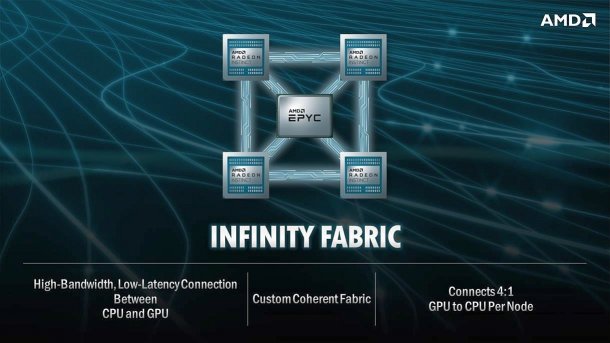

AMD Infinity Fabric

AMD hat ein besonderes Ass im Ärmel: Den schnellen Interconnect Infinity Fabric. Der kommt schon bisher in Zen-Prozessoren zum Einsatz, um mehrere Kern-Gruppen (CCX) intern zu koppeln oder auch zwei Epycs zu einem Zwei-Prozessor-System. Dazu lassen sich 64 der 128 PCI-Express-Lanes der Epycs in den Infinity-Fabric-Betriebsmodus umschalten. Auch die aktuellen 7-nm-Rechenbeschleuniger Radeon Instinct MI50 und MI60 nutzen Infinity Fabric, um mehrere davon zu koppeln.

Bei der kommenden Epyc-Generation mit Zen 2 ermöglicht AMD nun auch die Cache-kohärente Kopplung per Infinity Fabric zwischen einer Epyc-CPU und vier Radeon-GPUs. Details zu Transferrate und Latenz verrät AMD allerdings nicht. Ebenfalls ist derzeit offen, ob die von PCIe (4.0) auf Infinity Fabric umschaltbaren Epyc-Lanes auch noch andere Betriebsmodi beherrschen, etwa CCIX oder Gen-Z: AMD ist Mitglied in beiden Industriegremien.

Empfohlener redaktioneller Inhalt

Mit Ihrer Zustimmung wird hier ein externes YouTube-Video (Google Ireland Limited) geladen.

Ich bin damit einverstanden, dass mir externe Inhalte angezeigt werden. Damit können personenbezogene Daten an Drittplattformen (Google Ireland Limited) übermittelt werden. Mehr dazu in unserer Datenschutzerklärung.

Interconnect-Gerangel

Nvidia und IBM verbinden in den aktuellen Top500-Spitzenreitern Summit und Sierra die Tesla-V100-Beschleuniger mit den Power9-Prozessoren per NVLink 2.0 beziehungsweise OpenCAPI.

Intel plant für kommende Xeons und "Agilex"-FPGAs den kohärenten Interconnect Compute Express Link CXL auf Basis von PCI Express 5.0, also mit 32 GBit/s pro Lane. OpenCAPI 3.0 arbeitet derzeit mit 25 GBit/s, PCIe 4.0 mit 16 GBit/s. CCIX soll mit 25 GBit/s starten.

Für die Verbindung zwischen den einzelnen Cluster-Knoten verwendet Cray bei Shasta den Slingshot-Interconnect mit Dragonfly-(Libellen-)Topologie und 200 GBit/s pro Port. Mit dieser Rate läuft auch Infiniband HDR 200 Gb/s der Firma Mellanox, die Nvidia gekauft hat. Und auch Intel will die hauseigene und in "F"(abric-)Xeons eingebaute Omni-Path Architecture mit OPA200 auf diese Geschwindigkeit bringen.

(ciw)