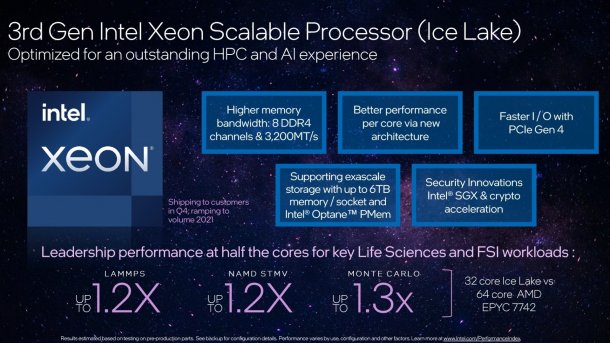

Intels "Ice Lake"-Xeons: Mit 32 Kernen schneller als AMD Epyc mit 64

Intels Serverprozessoren der dritten Xeon-SP-Generation sollen AMDs Epyc "Rome" überholen und ziehen in einige Supercomputer ein.

(Bild: Intel)

Auf der virtuellen Supercomputer-Konferenz SC'20 gibt Intel-Managerin Trish Damkroger einen Ausblick auf die dritte Xeon-SP-Generation "Ice Lake" und kündigt einige damit bestückte Supercomputer an.

Zudem bekräftigt Damkroger, dass noch 2021 erste Sapphire-Rapids-Xeons der vierten Xeon-SP-Generation kommen, die DDR5-Speicher sowie PCI Express 5.0 mit der kohärenten Erweiterung CXL für Rechenbeschleuniger bringen.

Im Rahmen des Exascale-Supercomputerprojekts Aurora haben Entwickler des Argonne National Laboratory (ANL) jetzt Zugriff auf frühe Prototypen von Xe-HP-Rechenbeschleunigern. Letztere sollen als Xe HPC alias "Ponte Vecchio" aus der 7-Nanometer-Fertigung in Aurora zum Einsatz kommen und sich per oneAPI programmieren lassen.

Videos by heise

Ice Lake-SP mit 32 Kernen

Die Ice-Lake-Xeon-SPs aus der 10-Nanometer-Fertigung kommen mit (mindestens) bis zu 32 Kernen, also nur mit vier mehr als die bisherigen Cascade-Lake-(14-Nanometer-)Typen (Xeon-SP Gen 2).

Allerdings hat Intel die Rechenleistung pro Takt bei den Ice-Lake-Rechenkernen gesteigert und im Vergleich zum AMD Epyc 7002 "Rome" haben sie statt nur zwei AVX2-Einheiten pro Kern AVX-512-Rechenwerke. Im Vergleich zu ihren Vorgängern haben die Ice-Lake-Xeons auch zwei RAM-Kanäle mehr (8 statt 6 bei LGA4189). In Supercomputing-Anwendungen wie NAMD STMV und LAMMPS zur Simulation von Molekulardynamik sollen 32 Ice-Lake-Kerne daher um 20 Prozent schneller rechnen als 64 AMD-Rome-Kerne. Bei der Monte-Carlo-Simulation verspricht Intel 30 Prozent Vorsprung. Allerdings plant AMD für 2021 die Einführung des Epyc "Milan" mit Zen-3-Technik.

Ice-Lake-Xeons bringen Intel-Server endlich auf den aktuellen PCI-Express-Stand mit PCIe 4.0.

Verwirrenderweise ordnet Intel die Ice-Lake-Xeons ebenso der dritten Xeon-SP-Generation zu wie die im Juni vorgestellten "Cooper Lake"-Prozessoren aus der 14-Nanometer-Fertigung. Die Ice Lakes sind aber vor allem für Server mit einem oder mit zwei Prozessoren (Single-/Dual-Socket) vorgesehen, die Cooper Lakes für welche mit vier und mehr CPU-Fassungen.

Anders als die Cooper-Lake-Xeons beherrschen die Ice Lakes das KI-Datenformat BFloat16 nicht, bringen aber eine Reihe anderer neuer Funktionen wie SGX2 und RAM-Verschlüsselung.

Neue Superrechner

Trish Damkroger erwähnte drei für 2021 geplante Supercomputer mit Ice Lake-SP: Die Korea Meterological Administration kauft ein 50-PFlops-System für Wetter- und Klimaberechnungen, das auf der aktuellen Top500-Liste in den Top-10 landen würde. Die deutsche Max Planck Computing & Data Facility (MPCDF) wird den "Raven" mit Nvidia A100 und rund 7 PFlops in Betrieb nehmen und Oracle will Ice Lake in seiner HPC-Cloud einsetzen.

(ciw)