PCI Express 6.0 und CXL 2.0 sollen Server umkrempeln

Durch hohe Transferraten, Switching, Cache-Kohärenz und weitere Funktionen ermöglichen PCIe 6.0 und CXL 2.0 neue Architekturen.

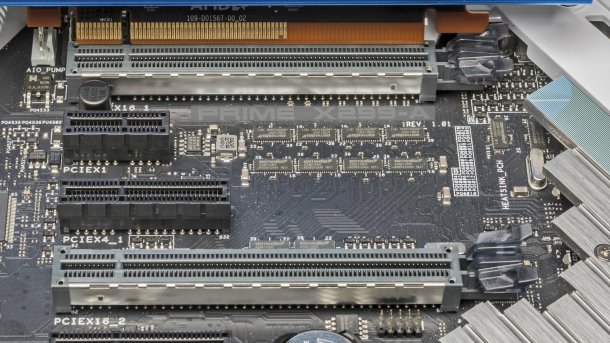

PCI-Express-Steckfassungen auf einem Mainboard

(Bild: c’t)

Die Industrievereinigung PCI SIG hat die Spezifikation für PCI Express 6.0 in der finalen Version 1.0 verabschiedet. Sie ist vor allem für Server und deren Komponenten wichtig, besonders im Verbund mit Compute Express Link (CXL).

PCIe 6.0 verdoppelt – wie bei PCIe-Generationswechseln üblich – die Datentransferrate im Vergleich zu PCIe 5.0 auf 64 Gigatransfers pro Sekunde, sodass eine einzige Lane (PCIe 6.0 x1) bis zu 8 GByte/s pro Richtung überträgt. Aktuelle PCIe-4.0-SSDs benötigen dazu vier Lanes.

Videos by heise

PCIe superschnell

Ein x16-Steckplatz bringt es mit PCIe 6.0 auf 128 GByte/s pro Richtung. Damit DMA-Transfers in dieser Geschwindigkeit möglich sind, braucht man vier DDR5-4800-Speicherkanäle, die zusammen über 150 GByte/s übertragen.

(Bild: Samsung )

Anders ausgedrückt: PCIe 6.0 x4 ist mit 32 GByte/s schneller als ein DDR4-3200-Speicherkanal mit 64 Datensignalleitungen. Das ermöglicht neue Architekturen wie disaggregierte Server, die sich je nach Rechenbedarf aus Ressourcenpools flexibel zusammenschalten lassen.

Schon für CXL 1.1 auf der Basis von PCIe 5.0 plant Samsung CXL-Speichermodule. Die erweiterten Funktionen von CXL 2.0 erleichtern es dann, nichtflüchtigen Speicher wie Optane DC Memory oder anderes Storage-Class Memory in Pools zu verwalten, die mehreren Serverknoten zugänglich sind.

Schnelleres PCIe ist auch für kommende SSDs sinnvoll, für KI-Rechenbeschleuniger sowie für Ethernetadapter mit 800 Gbit/s pro Port (800GE).

CXL könnte zudem den Einsatz neuartiger Konzepte wie RAM mit Rechenfunktionen oder Computational Storage beschleunigen sowie auch von SmartNICs beziehungsweise Data Processing Units (DPU, IPU, AWS Nitro).

| Datentransferraten von PCIe und RAM | |

| Schnittstelle | Transferrate |

| 4 Kanäle DDR5-4800 | 154 GByte/s |

| PCIe 6.0 x16 | 128 GByte/s |

| 2 Kanäle DDR5-4800 | 77 GByte/s |

| PCIe 6.0 x8 | 64 GByte/s |

| PCIe 5.0 x16 | 64 GByte/s |

| 1 Kanal DDR5-4800 | 38 GByte/s |

| PCIe 6.0 x4 | 32 GByte/s |

| PCIe 5.0 x8 | 32 GByte/s |

| PCIe 4.0 x16 | 32 GByte/s |

| 1 Kanal DDR4-3200 | 26 GByte/s |

| PCIe 6.0 x1 | 8 GByte/s |

| PCIe 4.0 x4 | 8 GByte/s |

| PCIe 3.0 x8 | 8 GByte/s |

| maximale Transferrate pro Richtung | |

PAM4-Modulation und FLITs

(Bild: Intel)

Um die extremen Datentransferraten zu erreichen, bringt PCIe 6.0 im Vergleich zu den Vorgängern gravierende Änderungen auf der physischen Ebene. So wird als Modulationsverfahren die vierstufige Pulsamplitudenmodulation (PAM4) eingesetzt, die statt einem (0 oder 1) nun zwei Bits pro Transfer überträgt, also mit vier Spannungspegeln arbeitet. Um die damit verbundene höhere Störanfälligkeit zu kompensieren, kommt als Fehlerkorrektur Forward Error Correction (FEC) zum Einsatz. Diese wiederum benötigt Datenpakete mit gleicher Länge, sogenannte Flow Control Units (FLITs).

PCIe-6.0-Fassungen bleiben aber abwärtskompatibel zu älteren PCIe-Versionen.

Server-Roadmap

(Bild: Intel)

Für 2022 hat Intel die vierte Generation des Xeon-SP als "Sapphire Rapids" mit PCIe 5.0 und CXL 1.1 angekündigt. Für Desktop-PCs ist bereits der Core i-12000 "Alder Lake" mit PCIe 5.0 auf dem Markt, allerdings ohne CXL. Auch der IBM Power10 beherrscht PCIe 5.0.

Um die hohen Datentransferraten zu verarbeiten, haben kommende Serverprozessoren mehr DRAM-Kanäle (AMD Genoa mit Zen 4, DDR5 und PCIe 5.0 etwa 12 statt 8) oder schnelles HBM2E-RAM (Intel Sapphire Rapids).

Für 2023 hat Intel die übernächste Generation von Serverprozessoren namens Granite Rapids angekündigt; ob sie PCIe 6.0 und CXL 2.0 bringt, ist aber unbekannt.

Das einst konkurrierende Interconnect-Konzept Gen-Z ist mittlerweile Geschichte. An CXL arbeiten seit 2019 auch ARM, AMD, IBM und Nvidia mit, die parallel eigene kohärente Interconnects wie CCIX, InfinityFabric, OpenCAPI und NVLink pflegen.

(ciw)